W25Q64是华邦公司推出的大容量SPI FLASH产品,其容量为64Mb。该25Q系列的器件在灵活性和性能方面远远超过普通的串行闪存器件。W25Q64将8M字节的容量分为128个块,每个块大小为64K字节,每个块又分为16个扇区,每个扇区4K个字节。W25Q64的最小擦除单位为一个扇区,也就是每次必须擦除4K个字节。所以,这需要给W25Q64开辟一个至少4K的缓存区,这样必须要求芯片有4K以上的SRAM才能有很好的操作。

W25Q64的擦写周期多达10W次,可将数据保存达20年之久,支持2.7~3.6V的电压,支持标准的SPI,还支持双输出/四输出的SPI,最大SPI时钟可达80Mhz。

W25Q64特征:

支持标准、双输出和四输出的SPI

高性能串行闪存

高达普通串行闪存性能的6倍

80Mhz的时钟操作

支持160Mhz的双输出SPI

支持320Mhz的四输出SPI

40MB/S的数据连续传输速率

高效的“连续读取模式”

低指令开销

仅需8个时钟周期处理内存

允许XIP操作

性能优于X16并行闪存

低功耗,温度范围宽

单电源2.7V至3.6V

4mA有源电流

-40°C 至+85°C的正常运行温度范围

灵活的4KB扇区构架

扇区统一擦除(4KB)

块擦除(32KB和64KB)

1到256个字节编程

超过10万次擦除/写循环

超过20年的数据保存

高级的安全功能

软件和硬件写保护

自上至下,扇区或块选择

锁定和保护OTP

每个设备都有唯一的64位ID

有效的空间的包装

8-pin SOIC 208-mil

8-pin PDIP 300-mil

8-pad WSON 8x6-mm

16-pin SOIC 300-mil

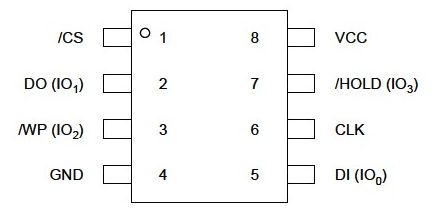

CS:片选信号输入

DO(IO1):数据输出(数据输入输出1)

WP(IO2):写保护输入(数据输入输出2)

GND:地信号

DI(IO0):数据输入(数据输入输出0)

CLK:串行时钟输入

HOLD(IO3):Hold输入(数据输入输出3)

VCC:电源

注:

- IO0和IO1用于标准SPI和双输出SPI操作

- IO0-IO3用于四输出SPI操作

片选:

SPI片选引脚能够使能和失能器件的操作。当片选引脚为高电平时,器件没有被选中,串行数据输出引脚(DO或IO0,IO2,IO3,IO4)处于高阻抗状态。当器件没有被选中时,其功耗将会处于待机状态下的水平,除非内部正在擦除、运行程序或状态寄存器周期。当片选引脚置为低时,器件被选中,电源消耗将增至活跃水平,可以进行读写操作。电源上电后,在执行一次操作之前,片选引脚必须由高电平转至低电平。

串行数据输入、输出:

W25Q64支持标准的SPI,双输出SPI和四输出SPI操作。标准的SPI指令利用单向的数据输入引脚在串行时钟输入上升沿串行地向器件写入指令、地址或数据。标准的SPI也利用单向的数据输出引脚在串行时钟输入下降沿串行地从器件读取数据或状态。

双输出和四输出SPI利用双向IO引脚在串行时钟输入上升沿串行地向器件写入指令、地址或数据,在串行时钟输入下降沿串行地从器件读取数据或状态。

写保护:

WP引脚用来防止状态寄存器被写入。用于与状态寄存器的块保护位(SEC、TB、BP2、BP1和BP0)配合,状态寄存器保护位(SRP),部分或整个存储器阵列可以用硬件保护。WP引脚在低电平时有效。当状态寄存器2的QE位设置为四倍I/O时,则WP(硬件写保护)功能不可用,因为此时这个引脚被用为IO2。

HOID:

HOID引脚允许器件在有效选择的情况下被终止。当HOLD引脚被置为低电平时,CS引脚为低,DO引脚将处于高阻态状态,并且DI和CLK引脚上的信号将被忽略。当HOLD引脚被置为高电平时,器件操作将被恢复。HOLD引脚的功能通常用在当多个器件共享同一个SPI信号的情况下。HOLD引脚在低电平时有效。当状态寄存器2的QE位设置为四倍I/O时,则HOLD引脚功能不可用,因为此时这个引脚被用为IO3。

串行时钟(CLK):

SPI串行时钟输入引脚(CLK)为串行输入和输出操作提供时序。

本文由 谭文龙 创作,采用 知识共享署名4.0 国际许可协议进行许可

本站文章除注明转载/出处外,均为本站原创或翻译,转载前请务必署名

最后编辑时间为: Jun 25, 2020 at 08:17 am